发布时间:2021-09-23所属分类:电工职称论文浏览:1次

摘 要: 摘要:远探测方位反射声波成像测井仪(BAR)是新一代成像测井仪,其测井数据存储于内部大容量存储模块中;为了实现在测井现场快速读取和回放测井数据,设计了一种基于USB总线的数据读取接口;数据读取接口通过USB总线与PC通讯,通过自定义高速串行总线与下井仪数

摘要:远探测方位反射声波成像测井仪(BAR)是新一代成像测井仪,其测井数据存储于内部大容量存储模块中;为了实现在测井现场快速读取和回放测井数据,设计了一种基于USB总线的数据读取接口;数据读取接口通过USB总线与PC通讯,通过自定义高速串行总线与下井仪数据存储模块通讯;高速串行总线为基于M-LVDS的差分总线,设计的工作频率为80MHz,采用8B/10B编码;数据读取接口电路采用FPGA作为主控芯片,高速总线协议和传输控制均在FGPA中实现;所设计数据读取接口已实现8口井的现场测井数据读取,数据读取速度达到57Mbps;该设计实现了测井数据的现场快速读取和回放,保证了测井数据检验的时效及测井施工的效率。

关键词:远探测方位反射声波成像测井仪;高速差分总线;8B/10B;现场可编程门阵列;并行控制逻辑

0引言

随着勘探开发的不断深入,远离井壁周围空间的探测成为迫切需要的勘探技术[13],中国石油大学(北京)与中国石油集团合作研制的基于相控阵技术[46]的远探测方位反射声波成像测井仪(BAR)[78]成功实现了带方位分辨能力的远离井壁地质空间的探测。为实现方位分辨能力,BAR采用了阵列化的探测器结构(传感器数量达80个);为实现远距离探测,BAR每个传感器数据采样深度可达8k,因此,每个深度点总数据量可达1.2MB。而现今成熟的电缆测井遥传系统最高通讯速度不超过1Mbps[910]。

为解决遥传通讯速度低的瓶颈,BAR采用了“井下存储,抽样上传”的工作方式,即所有测井数据均存储于井下大容量存储器内,仅抽样部分关键数据上传到地面[11]。在BAR仪器上提到井口后,需要在现场快速读取测井数据,通过回放分析软件快速验证测井施工质量是否合格。常规的测井地面系统不具备专用高速数据读取接口,因此,需要开发专用的数据读取接口,以实现BAR数据的现场快速读取和回放分析。另外,数据读取接口应具备独立供电能力,可以实现井下数据存储电路的供电。

本文设计了一种基于USB总线的远探测方位反射声波成像测井仪数据读取接口,实现了在井场对BAR主控短节内的数据存储电路供电和测井数据的快速读取与回放、以及测井质量的检验。

1数据读取接口整体设计

BAR测井仪的主控短节内的数据存储模块的供电为9~15V,常温下功耗不超过2W,数据存储模块物理读取速度不高于10MB/s,经过本地文件系统处理后,数据输出速度约为8MB/s。本设计中选用USB2.0接口,即可以满足通讯要求,也可以为接口电路供电。接口电路与井下仪器数据存储模块的物理连接距离为3~5m,且二者通过31芯测井连接器相连,引线资源有限;另外,井场环境还存在各种强电干扰。因此,接口电路与井下仪器数据存储模块的通讯选用多点低电压差分信号(M-LVDS)来构建高速串行总线[1213]。

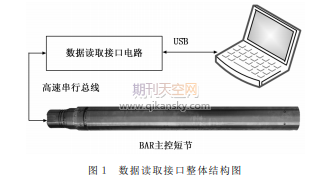

数据读取接口整体结构如图1所示。数据读取接口主要由运行于上位机的控制软件和接口电路两部分组成。其中,硬件接口电路实现BAR数据存储模块数据输出接口和计算机接口的转换。控制软件实现数据读取过程的控制、数据存储、数据解编和数据回放。上位机通过USB总线控制数据读取接口板,数据读取接口电路根据上位机命令通过基于M-LVDS的高速串行总线读取井下数据。

2数据读取接口电路硬件设计

数据读取接口电路主要由锂电池、电源管理电路、电流检测电路、USB总线控制器、FPGA和高速总线驱动器等组成,其结构如图2所示。其中,电源管理电路实现将USB供电转换为数据读取接口电路内各电路所需要的低压电平,如3.3V、1.2V等。另外,电源管理电路将锂电池的输出升压转换为15V输出,给BAR主控短节内的数据存储模块供电。电流检测电路用于精确检测数据存储模块的供电电流。根据数据存储模块的供电电流可以对存储模块的故障进行初步判断。

USB控制器实现数据读取接口电路和主机间的通讯,本设计中选用FTDI公司的FT232H[14],该芯片以内部固件实现了整个USB协议,最高通讯速度可以达到40MB/s。本设计中将FT232H配置成USB转异步并行FIFO模式,在此模式下,FT232H内置一个双向FIFO接口,通过读写标志信号和读写使能信号与FPGA进行通讯。

为了保证数据读取接口电路通讯的高效,前端控制器采用FPGA芯片作为主控制芯片。本设计中FPGA实现数据编码、解码、校验、数据缓存、高速串行总线控制等。与微处理器MCU中指令顺序执行所不同的是,FPGA中大量的门阵列可以实现复杂的并行逻辑控制功能,可以以流水线的方式实现数据的编码、校验和缓存等,提高总线响应的时效。以FPGA为控制核心也便于升级和扩展。

高速总线驱动器实现TTL电平和M-LVDS电平的转换。

3数据读取接口电路软件设计

3.1传输格式

井下仪器与数据读取电路的通讯和数据读取电路与上位机的通讯均采用相同的帧格式,具体格式如图3所示。一个完整的通讯帧包括帧头、帧类型、帧内容和校验码。根据传输数据长度的不同将通讯帧分为两类,一种是短帧,总长度规定为16字节,用于传输命令和井下仪器供电电流值等;一种是长帧,总长度固定为2048字节,仅用于传输井下仪器上传数据。

3.2控制逻辑设计

数据读取接口电路的软件是运行在FPGA内的逻辑电路,采用VHDL语言进行设计,图4为控制逻辑结构框图。FPGA内的逻辑电路主要由USB并行接口、命令解析、下传命令集、8B/10B编码、串行发送器、总线驱动控制器、串行接收器、10B/8B解码、数据校验、数据缓存、上传命令集、供电管理、电流采集控制、电流缓存器等逻辑功能模块组成。

USB并行接口模块由USB数据读取功能模块和USB数据写入功能模块组成,其中USB数据读取功能模块是根据FT232H的接收数据指示信号RXF,读取上位机发送到FT23H内部FIFO中的下传数据,而后发送该数据到命令解析功能模块。USB数据写入功能模块是跟据FT232H发送指示信号TXF,在状态控制器的控制下,将选择缓存数据或电流测量值或命令集内的数据发送到FT232H中的发送FIFO中。

命令解析模块的功能是根据接收命令的内容产生相应的控制指示信号,用于驱动状态控制器状态的转换,并将需要下传的命令写入到下传命令集中。

下传命令集为数据读取接口电路下发到井下仪器主控短节的命令集合,其包括两部分,一部分是与井下仪器通讯的握手命令,如下传数据请求命令、下传数据重发命令等,该类命令以ROM形式固化在FPGA内;另一部分是由数据读取接口电路转发给井下仪器的上位机命令,缓存在FPGA内的双口RAM中。

数据读取接口电路与井下仪器主控短节通过差分串行总线通讯,为提高数据传输的可靠性,二者间的通讯采用了8B/10B编码方法。8B/10B编码方法是通过冗余的2bits实现传输的数据流中‘0’和‘1’的数量均等。该编码方法保证数据流中有足够的电平转换,既可以实时校正串行接收电路的时钟漂移,又可以保证直流平衡,从而保证数据传输的高可靠性。另外,额外的冗余编码还可以用于数据错误识别,提高传输的校验能力。FPGA是基于查找表结构,且有大量的内部存储空间,因此,本设计中8B/10B编码和10B/8B解码模块均采用查表法实现,在串行发送和接收时同步实现编码和解码,提高传输效率。

数据解析及校验模块是根据数据传输协议的约定解析命令及校验接收到数据的正确性,并将命令类型及校验结果通知状态控制器。本设计中采用CRC-7校验,校验码采用查表方式获得,可以在一个时钟周期内得到校验码,从而可以与串行接收器及数据缓存器同步工作,同步实现数据的接收、校验和缓存。

数据缓存模块主要用于缓存井下仪器上传数据和电流采集数据,该数据缓存基于FPGA内的SRAM实现,分为3个双端口SRAM区。其中电流采集数据缓存区占用一个SRAM区,采用循环写入模式。井下仪器上传数据缓存区占用为两个SRAM区,采用乒乓结构。

上传命令集为数据读取电路发送到上位机的命令的集合,该命令集以ROM形式固化在FPGA内。

状态控制器是数据读取接口电路的核心,其根据上位机的下发命令、井下仪器上传数据状态和数据读取接口电路的状态,产生相应的控制信号,实现命令下发及命令和数据上传的功能。状态控制器主要由下传控制状态机和上传控制状态机组成。下传控制状态机主要包括供电设置态、下传命令态和设置上传命令态,具体转换关系如图5(a)所示,其中,设置上传命令状态的作用是产生驱动上传控制状态机状态转换的控制信号。上传控制状态机主要状态有上传电流值态、上传命令态和上传数据态,具体转换关系如图5(b)所示,其中,上传数据态包含等待子状态,仅当数据传输完成后退出上传数据态。

基于硬件描述语言设计的控制逻辑实现了上位机命令的解析、命令编码下传、上传数据同步接收、同步解码和校验等,纯硬件逻辑使各部分同步协调工作,可以实现高效的数据传输。图6为下传命令和上传数据的仿真波形图。图中,数据读取电路在接收到上传数据后的5个时钟周期内开始发送下传命令,可以看出纯逻辑电路响应高效迅速。

4上位机软件设计

上位机软件的功能是通过下发命令控制数据读取接口电路读取井下仪器的测井数据、存储和回放测井数据并将测井数据转换为测井评价软件能识别的标准格式文件。

上位机软件基于VisualStudio2005实现,其组成结构如图7所示。控制软件主要由数据读取、电流监控、数据存储、文件转换和回放显示等功能模块组成,以上功能模块均在独立的线程中实现。

相关知识推荐:电子测量工程师报考条件有哪些

数据读取线程的主要功能是通过调用D2XX驱动程序控制数据读取电路与井下仪器数据存储模块进行通讯,实现井下仪器数据的连续读取,并将接收到的数据发送给数据存储线程。另外,数据读取线程还负责控制清空井下仪器数据存储模块。

数据存储线程主要负责井下上传数据的重整、错误校正和存储。井下上传数据包括井下仪器工作状态信息和原始波形数据。数据存储线程将上传数据存储为原始数据文件,同时提取仪器工作状态信息并以文本格式存储到一个独立的状态文件,将声波波形数据以二进制格式存储到另一个独立的测井数据文件。

文件转换线程主要实现声波测井数据的增益还原、深度还原和标准格式的转换,以提供符合各测井解释平台格式要求的测井数据文件。由于测井数据文件较大,普通的IO文件操作方式效率较低下,本设计中采用了内存映射文件方式实现测井数据文件的读取和标准格式文件的写入。

电流监控线程是在数据读取过程中定时读取和记录井下仪器数据存储模块的供电电流。通过井下仪器数据存储模块供电电流的异常,可以初步预测井下仪器数据存储模块失效概率,并为数据存储模块的失效分析提供支撑。

5实验结果与分析

所研制的远探测声波测井仪数据读取接口已成功应用测井现场,累计完成8口井的现场数据读取。在BAR测井仪的井下工作结束后,仪器上提到井口,利用该数据读取接口将测井数据快速读取到计算机中。自定义高速串行总线(M-LVDS总线)实现数据读取接口与测井仪主控短节的通信,原始测井数据以80Mbps的速率传输到FPGA中进行通讯协议的解编和校验。校验成功的数据由USB总线上传到测井计算机中,由上位机软件进行回放。

图8为原始数据传输过程中高速串行总线波形图,图中通道1为数据读取接口电路总线驱动的发送使能信号,通道3为M-LVDS+,通道2为M-LVDS-。从图中可以看出,差分总线速率为80Mbps。在接收到上传数据后,数据读取接口电路延时350ns左右即启动命令下传。可以看出,基于硬件逻辑的并行化协议管理方法保证了高速串行总线上下行的快速切换,也保证串行总线的高速率。

新疆塔里木油田某口井的测井数据为720MB,读取时间为101s,则平均读取速度达到了57Mbps,略低于理论数据读取速率。经观测发现,在某些时候井下数据存储模块在接收到数据请求命令后的响应存在不定延时。这主要是因为井下数据存储模块在读取数据过程中首先进行分块校验,如果出现错误则需要根据冗余信息校正错误,因此出现响应延时,降低了整体数据读取速度。

图9为测井现场井口数据回放界面图。该次施工测井井段为3808.82~3556.32m,波形数据质量良好。

6结束语

本文设计了一种基于USB总线和高速串行总线的测井数据读取接口。本设计采用FPGA作为控制核心,基于硬件描述语言设计的控制逻辑实现了上位机命令的解析、命令编码下传、上传数据同步接收、同步解码和校验等,纯硬件逻辑使各部分同步协调工作,实现了高效的数据传输。经测试,该数据读取接口的平均数据读取速率达57Mbps,实现了测井数据的现场快速读取和回放,保证了测井数据检验的时效及测井施工的效率。——论文作者:谢超1,2,门百永1,2,幺永超3,卢俊强1,2,王邦伟4,刘先平5

SCISSCIAHCI